#### DOCTOR OF PHILOSOPHY

FPGA-based programmable embedded platform for image processing applications

Siddiqui, Fahad Manzoor

Award date: 2018

Awarding institution: Queen's University Belfast

Link to publication

#### Terms of use

All those accessing thesis content in Queen's University Belfast Research Portal are subject to the following terms and conditions of use

- Copyright is subject to the Copyright, Designs and Patent Act 1988, or as modified by any successor legislation

- Copyright and moral rights for thesis content are retained by the author and/or other copyright owners

A copy of a thesis may be downloaded for personal non-commercial research/study without the need for permission or charge

Distribution or reproduction of thesis content in any format is not permitted without the permission of the copyright holder

- · When citing this work, full bibliographic details should be supplied, including the author, title, awarding institution and date of thesis

#### Take down policy

A thesis can be removed from the Research Portal if there has been a breach of copyright, or a similarly robust reason If you believe this document breaches copyright, or there is sufficient cause to take down, please contact us, citing details. Email: openaccess@qub.ac.uk

#### Supplementary materials

Where possible, we endeavour to provide supplementary materials to theses. This may include video, audio and other types of files. We endeavour to capture all content and upload as part of the Pure record for each thesis.

Note, it may not be possible in all instances to convert analogue formats to usable digital formats for some supplementary materials. We exercise best efforts on our behalf and, in such instances, encourage the individual to consult the physical thesis for further information.

Download date: 21. May. 2024

# FPGA-based Programmable Embedded Platform for Image Processing Applications

### Fahad Manzoor Siddiqui

School of Electronics, Electrical Engineering and Computer Science

Queen's University Belfast

A thesis submitted for the degree of

Doctor of Philosophy

September 11, 2018

#### Abstract

A vast majority of electronic systems including medical, surveillance and critical infrastructure employs image processing to provide intelligent analysis. They use onboard pre-processing to reduce data bandwidth and memory requirements before sending information to the central system. Field Programmable Gate Arrays (FPGAs) represent a strong platform as they permit reconfigurability and pipelining for streaming applications. However, rapid advances and changes in these application use cases crave adaptable hardware architectures that can process dynamic data workloads and be easily programmed to achieve efficient solutions in terms of area, time and power.

FPGA-based development needs iterative design cycles, hardware synthesis and place-and-route times which are alien to the software developers. This work proposes an FPGA-based programmable hardware acceleration approach to reduce design effort and time. This allows developers to use FPGAs to profile, optimise and quickly prototype algorithms using a more familiar software-centric, edit-compile-run design flow that enables the programming of the platform by software rather than high-level synthesis (HLS) engineering principles.

Central to the work has been the development of an optimised FPGAbased processor called Image Processor (IPPro) which efficiently uses the underlying resources and presents a programmable environment to the programmer using a dataflow design principle. This gives superior performance when compared to competing alternatives. From this, a three-layered platform has been created which enables the realisation of parallel computing skeletons on FPGA which are used to efficiently express designs in high-level programming languages. From bottom-up, these layers represent programming (actor, multiple actors and parallel skeletons) and hardware (IPPro core, multicore IPPro, system infrastructure) abstraction. The platform allows acceleration of parallel and non-parallel dataflow applications.

A set of point and area image pre-processing functions are implemented on Avnet Zedboard platform which allows the evaluation of the performance. The point function achieved 2.53 times better performance than the area functions and point and area functions achieved performance improvements of 7.80 and 5.27 times over single core IPPro by exploiting data parallelism. The pipelined execution of multiple stages revealed that a dataflow graph can be decomposed into balanced actors to deliver maximum performance by hiding data transfer and processing time through exploiting task parallelism; otherwise, the maximum achievable performance is limited by the slowest actor due to the ripple effect caused by unbalanced actors. The platform delivered better performance in terms of fps/Watt/Area than Embedded Graphic Processing Unit (GPU) considering both technologies allows a software-centric design flow.

#### Acknowledgements

I would like to express my profound gratitude to my supervisor, Prof. Roger Woods for giving me the opportunity to undertake part-time research and in providing me continuous advice, supervision and encouragement throughout my research. I am grateful for his systematic guidance, comprehensive reviews and critical feedback to improve this thesis. In addition, I am grateful to Dr. Karen Rafferty for providing additional support, reasoning and constructive criticism for my research. I want to thank Prof. Sakir Sezer for supporting me in finishing the thesis.

I would like to thank my colleagues at Queen's University Belfast with whom I worked during my PhD including Dr. Burak Bardak and Dr. Moslem Amiri with whom I worked on the Rathlin project, for sharing their ideas and knowledge to improve my research activities. Particular thanks go to Dr. Matthew Milford, Dr. Colm Kelly, Umar Ibrahim Minhas and Tiantai Deng for sharing application use case results to optimise and improve the platform architecture.

A warm thanks to Margarita Magdenko for her continuous moral support, encouragement and affection. Above all, I would like to thank my parents who have given me the strength and wisdom to be sincere in my work, for setting high moral standards, supporting me through their hard work and their unconditional love and affection.

# Table of Contents

| Ta | able  | of Con | tents                                       | V                      |

|----|-------|--------|---------------------------------------------|------------------------|

| Li | st of | Table  | s                                           | x                      |

| Li | st of | Figur  | es                                          | $\mathbf{x}\mathbf{v}$ |

| 1  | Intr  | oduct  | ion                                         | 1                      |

|    | 1.1   | Resear | rch problem                                 | 2                      |

|    | 1.2   | Rathli | in Project                                  | 4                      |

|    | 1.3   | Propo  | sed approach                                | 5                      |

|    | 1.4   | Thesis | s Contributions                             | 8                      |

|    | 1.5   | Thesis | s Outline                                   | 10                     |

| 2  | Bac   | kgrou  | $\mathbf{nd}$                               | 13                     |

|    | 2.1   | Parall | el embedded architectures                   | 14                     |

|    |       | 2.1.1  | FPGA multiprocessor system-on-chip          | 14                     |

|    |       | 2.1.2  | FPGA hardware accelerator design approaches | 15                     |

|    |       | 2.1.3  | Need for adaptable hardware architectures   | 19                     |

|    |       | 2.1.4  | FPGA memory and computation resources       | 20                     |

|   |     | 2.1.5 DSP block                                            | 22 |

|---|-----|------------------------------------------------------------|----|

|   | 2.2 | Dataflow model of computation                              | 23 |

|   |     | 2.2.1 Notion of parallelism in dataflow graphs             | 24 |

|   |     | 2.2.2 Dataflow transformation                              | 25 |

|   | 2.3 | Parallel computing skeletons                               | 25 |

|   |     | 2.3.1 Pipeline                                             | 26 |

|   |     | 2.3.2 Split, compute and merge                             | 26 |

|   |     | 2.3.3 Farm                                                 | 27 |

|   | 2.4 | Related work on FPGA soft processors                       | 28 |

|   |     | 2.4.1 Scalar Processors                                    | 29 |

|   |     | 2.4.2 Multicore Processors                                 | 30 |

|   |     | 2.4.3 DSP Slice Processors                                 | 35 |

|   | 2.5 | Summary                                                    | 36 |

| 3 | Rat | hlin Project                                               | 39 |

|   | 3.1 | Rathlin Objectives                                         | 40 |

|   | 3.2 | Programming workflow                                       | 41 |

|   | 3.3 | Cal Actor Language (CAL)                                   | 42 |

|   |     | 3.3.1 Semantics and execution model                        | 43 |

|   | 3.4 | Producer-consumer computing                                | 45 |

|   | 3.5 | Summary                                                    | 46 |

| 4 | Ima | age Processing Processor (IPPro)                           | 48 |

|   | 4.1 | Introduction                                               | 48 |

|   | 4.2 | Algorithmic characteristics of image processing algorithms | 51 |

|   | 43  | Exploration of efficient FPGA soft-core processor          | 52 |

|   |     | 4.3.1   | Balance between compute and memory resources                | 53         |

|---|-----|---------|-------------------------------------------------------------|------------|

|   |     | 4.3.2   | FPGA-based soft-core processor functionality vs performance |            |

|   |     |         | trade-off                                                   | 56         |

|   | 4.4 | Image   | Processing Processor (IPPro)                                | 61         |

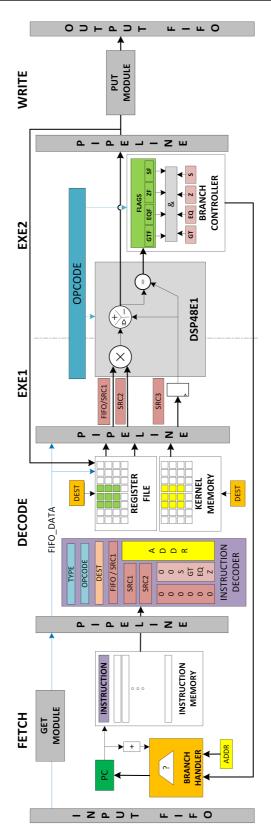

|   |     | 4.4.1   | Datapath                                                    | 63         |

|   |     | 4.4.2   | Branch and conditional execution                            | 64         |

|   |     | 4.4.3   | Instruction set architecture                                | 65         |

|   |     | 4.4.4   | Pipelined stream processing                                 | 65         |

|   |     | 4.4.5   | Dataforwarding                                              | 66         |

|   |     | 4.4.6   | Implementation results                                      | 68         |

|   | 4.5 | IPPro   | Optimisations                                               | 69         |

|   |     | 4.5.1   | Minimum and maximum instructions                            | <b>7</b> 0 |

|   |     | 4.5.2   | Coprocessor extension                                       | 71         |

|   | 4.6 | Comp    | arison of IPPro results                                     | 74         |

|   | 4.7 | Applic  | cation use cases                                            | <b>7</b> 5 |

|   |     | 4.7.1   | System architecture                                         | <b>7</b> 9 |

|   |     | 4.7.2   | Comparison of IPPro with HLS approach                       | 82         |

|   |     | 4.7.3   | Comparison of IPPro against programmable FPGA-based         |            |

|   |     |         | architecture                                                | 83         |

|   |     | 4.7.4   | Comparison of IPPro with MicroBlaze                         | 84         |

|   | 4.8 | Summ    | ary                                                         | 85         |

|   | T   |         |                                                             | 0.0        |

| 5 | IPF | 'ro-bas | sed acceleration of dataflow actor                          | 88         |

|   | 5.1 | Introd  | uction                                                      | 88         |

|   | 5.2 | IPPro   | : A dataflow processor                                      | 90         |

|   |     | 5.2.1  | Notion of firing an actor                                    | 92         |

|---|-----|--------|--------------------------------------------------------------|------------|

|   |     | 5.2.2  | Producer-consumer computing model                            | 94         |

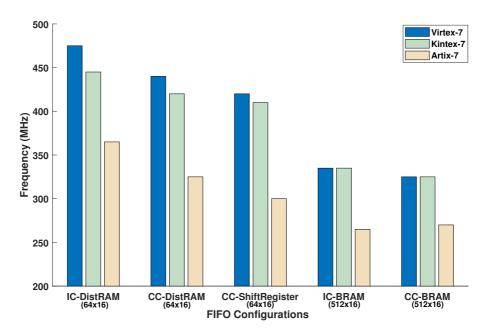

|   |     | 5.2.3  | Evaluation of FIFO configurations                            | 95         |

|   |     | 5.2.4  | Mapping and execution of static dataflow actor               | 97         |

|   |     | 5.2.5  | Supporting multi-port dataflow actor                         | 99         |

|   |     | 5.2.6  | Discussion on hardware acceleration using IPPro over HLS     | 101        |

|   | 5.3 | Manag  | gement and provisioning of IPPro hardware accelerators       | 103        |

|   | 5.4 | Datafl | ow parallelism and multiple IPPro                            | 108        |

|   |     | 5.4.1  | Configurable data distribution and collection architecture . | 111        |

|   | 5.5 | Case S | Study: $k$ -means clustering                                 | 115        |

|   |     | 5.5.1  | MPSoC-based heterogeneous system architecture                | 117        |

|   |     | 5.5.2  | IPPro hardware accelerator designs                           | 118        |

|   |     | 5.5.3  | Acceleration results                                         | 120        |

|   |     | 5.5.4  | Comparison against GPU implementations                       | 122        |

|   | 5.6 | Summ   | ary                                                          | 126        |

| 6 | FPO | GA-ba  | sed programmable hardware acceleration platform              | <b>128</b> |

|   | 6.1 | Introd | luction                                                      | 128        |

|   | 6.2 | Progra | ammable realisation of parallel skeletons on FPGAs           | 131        |

|   | 6.3 | IPPro  | core architectural optimisations                             | 132        |

|   |     | 6.3.1  | Dataflow actor firing rule optimisation                      | 133        |

|   |     | 6.3.2  | Scratchpad memory to access non-streaming data               | 136        |

|   |     | 6.3.3  | Host management of IPPro core using AMBA-AXI4                | 138        |

|   |     | 6.3.4  | Implementation results of optimised IPPro core               | 140        |

|   | 6.4 | Multio | core IPPro                                                   | 141        |

|    |       | 6.4.1   | Exploration of multicore interconnect architecture           | 142 |

|----|-------|---------|--------------------------------------------------------------|-----|

|    |       | 6.4.2   | Impact of interconnect's core connectivity and core utilisa- |     |

|    |       |         | tion on area and performance                                 | 145 |

|    |       | 6.4.3   | Multicore IPPro architecture                                 | 150 |

|    |       | 6.4.4   | Example: Mapping of dataflow graph onto multicore archi-     |     |

|    |       |         | tecture                                                      | 151 |

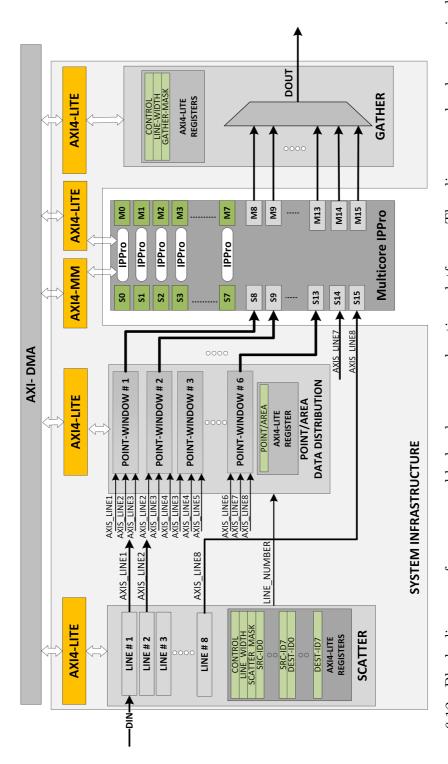

|    | 6.5   | FPGA    | a-based programmable hardware acceleration platform          | 153 |

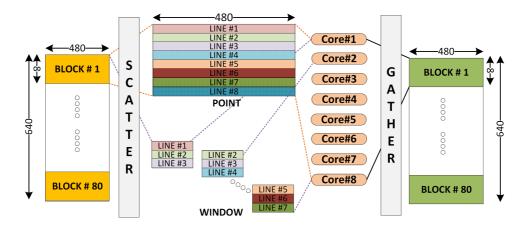

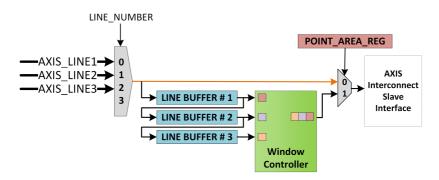

|    |       | 6.5.1   | Parallel distribution and collection of data streams         | 153 |

|    |       | 6.5.2   | Implementation results                                       | 159 |

|    | 6.6   | Paralle | el implementation of image pre-processing functions          | 160 |

|    |       | 6.6.1   | Performance analysis                                         | 163 |

|    | 6.7   | Summ    | ary                                                          | 170 |

| 7  | Con   | clusio  | n and Future Work                                            | 172 |

|    | 7.1   | Summ    | ary                                                          | 172 |

|    | 7.2   | Thesis  | Contributions                                                | 173 |

|    | 7.3   | Sugges  | stions for further work                                      | 177 |

| A  | Aut   | hor's   | Publications                                                 | 180 |

| В  | IPP   | ro: Te  | echnical details                                             | 182 |

| Bi | bliog | graphy  |                                                              | 185 |

# List of Tables

| 2.1 | High-level Synthesis (HLS) tools for FPGAs                          | 18 |

|-----|---------------------------------------------------------------------|----|

| 3.1 | Dataflow semantics and their functional requirements to imple-      |    |

|     | ment on a hardware architecture                                     | 44 |

| 4.1 | Categorisation of image processing operations based on their mem-   |    |

|     | ory and execution patterns                                          | 51 |

| 4.2 | Memory and compute resources in 28nm Xilinx FPGA technology.        | 55 |

| 4.3 | Correlation of FPGA-based soft-core datapath and dataflow mod-      |    |

|     | els with increasing functionality and memory.                       | 58 |

| 4.4 | Details of supported dataflow features and processor datapath mem-  |    |

|     | ory elements in each presented model                                | 58 |

| 4.5 | IPPro instruction frame structure                                   | 65 |

| 4.6 | IPPro supported addressing modes and instructions                   | 65 |

| 4.7 | IPPro code to implement $func$ with and without data<br>forwarding  | 67 |

| 4.8 | IPPro implementation results on selected Xilinx development boards. | 68 |

| 4.9 | Implementation of Min/Max using native and optimised IPPro          |    |

|     | instructions                                                        | 71 |

#### LIST OF TABLES

| 4.10 | Implementation results of optimised IPPro datapath to support     |            |

|------|-------------------------------------------------------------------|------------|

|      | coprocessor extension on ZC706 (Kintex-7)                         | 73         |

| 4.11 | Comparison of IPPro against other FPGA-based soft-core proces-    |            |

|      | sor architectures                                                 | 75         |

| 4.12 | Mathematical representation of image pre-processing functions     | <b>7</b> 6 |

| 4.13 | Area utilisation results of IPPro hardware accelerator            | 81         |

| 4.14 | Comparison of hardware acceleration results obtained from HLS     |            |

|      | and IPPro using Avnet Zedboard (Artix-7)                          | 82         |

| 4.15 | Comparison of IPPro performance results against programmable      |            |

|      | FPGA-based architecture                                           | 83         |

| 4.16 | Area comparison of IPPro against programmable FPGA-based ar-      |            |

|      | chitecture. The normalised per core resource utilisation are re-  |            |

|      | ported in the brackets                                            | 84         |

| 4.17 | Comparison of micro-benchmarks on IPPro and MicroBlaze            | 84         |

| 4.18 | Area comparison of IPPro and MicroBlaze processors                | 85         |

| 5.1  | One-to-one mapping of dataflow semantics onto IPPro datapath      | 91         |

| 5.2  | IPPro code implementing dataflow actor firing rule                | 93         |

| 5.3  | Implementation results of processor datapath using different FIFO |            |

|      | configurations on Artix-7 FPGA fabric                             | 97         |

| 5.4  | Hardware resource and control requirements to map multi-port      |            |

|      | actors onto IPPro core                                            | 100        |

| 5.5  | Impact of accelerator classes on IPPro-based core, multicore and  |            |

|      | system requirements                                               | 104        |

#### LIST OF TABLES

| 5.6  | IPPro-based multiple core architectures and their impact on sys-                            |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | tem requirements and inter-core communication                                               | 106 |

| 5.7  | Impact on area utilisation of different accelerator configurations                          | 108 |

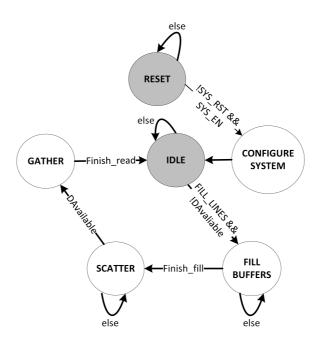

| 5.8  | Output signals of FSM for each state                                                        | 114 |

| 5.9  | Summary of the C functions running on the host processor to pro-                            |     |

|      | gram and control the underlying architecture                                                | 118 |

| 5.10 | Dataflow actor mapping and supported parallelism of IPPro hard-                             |     |

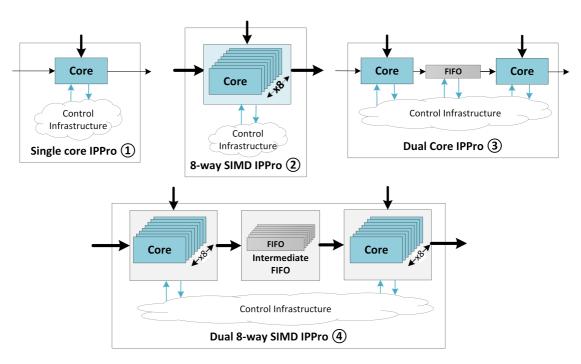

|      | ware accelerator design presented in Figure 5.15                                            | 120 |

| 5.11 | Performance measurements for design $\textcircled{1}$ and $\textcircled{2}$ of Figure 5.15. | 120 |

| 5.12 | FPGA area utilisation of various designs shown in Figure 5.15.                              |     |

|      | The relative Zedboard area utilisation is also reported                                     | 121 |

| 5.13 | Performance with task-level parallelism using designs in Figure 5.15.                       | 121 |

| 5.14 | Power, resource and combined efficiency comparisons of IPPro-                               |     |

|      | based $k$ -means implementations on Zedboard                                                | 124 |

| 5.15 | Power, resource and combined efficiency comparisons for $k$ -means                          |     |

|      | using Xilinx Zynq XC7Z045 Kintex-7 FPGA and GPU NVIDIA                                      |     |

|      | GTX980                                                                                      | 124 |

| 6.1  | IPPro instructions to access scratchpad memory                                              | 137 |

| 6.2  | Implementation results of the optimised IPPro on Kintex-7 fabric.                           |     |

| 6.3  | Comparison of IPPro against other FPGA-based soft-core processors.                          | 141 |

| 6.4  | Implementation results to evaluate scaling of 4x4 and stream in-                            |     |

|      | terconnect architectures on area and core utilisation to realise data                       |     |

|      | (vertical) and task (horizontal) parallel implementations                                   | 148 |

| 6.5  | Normalised area utilisation numbers of 4x4 with respect to stream   |     |

|------|---------------------------------------------------------------------|-----|

|      | interconnect realising parallel implementations                     | 148 |

| 6.6  | Implementation results of scaled-up stream interconnect designs     |     |

|      | with increasing core-connectivity on Artix-7 and Kintex-7 fabrics.  |     |

|      | The normalised area utilisation numbers of each design with re-     |     |

|      | spect to single-core IPPro are reported within the brackets         | 148 |

| 6.7  | The AXI4-Lite (control) register map of platform hardware modules.  | 157 |

| 6.8  | Area utilisation results of the system infrastructure               | 159 |

| 6.9  | Estimation of number of multicore IPPro on Xilinx Zynq MPSoCs.      | 160 |

| 6.10 | Formal mathematical representation of chosen image pre-processing   |     |

|      | functions.                                                          | 161 |

| 6.11 | Data parallel performance results of point and area functions using |     |

|      | IPPro on Artix-7 (Zedboard)                                         | 165 |

| 6.12 | Comparison of data parallel implementation of point functions us-   |     |

|      | ing IPPro against ARM (-O2,-O3)                                     | 165 |

| 6.13 | Comparison of data parallel implementation of area functions using  |     |

|      | IPPro against ARM (-O2,-O3)                                         | 165 |

| 6.14 | Implementation results of HLS generated IPs on Kintex-7 fabric.     |     |

|      | (Normalised area and performance results of multicore IPPro to      |     |

|      | HLS)                                                                | 167 |

| 6.15 | Performance results of task parallel implementations of multiple    |     |

|      | dataflow actors on multicore IPPro                                  | 168 |

| 6.16 | Performance results of heterogeneous decomposed compute func-       |     |

|      | tions using multicore IPPro                                         | 169 |

#### LIST OF TABLES

| B.1 | IPPro supported instruction set and their corresponding DSP48E1 |     |

|-----|-----------------------------------------------------------------|-----|

|     | control signals.                                                | 182 |

| B.2 | IPPro instruction set                                           | 183 |

| B.3 | The AXI4-Lite control register map                              | 184 |

# List of Figures

| 1.1  | Hierarchical illustration of hardware and software abstraction sup-     |    |

|------|-------------------------------------------------------------------------|----|

|      | ported by each layer of the proposed programmable hardware ac-          |    |

|      | celeration architecture                                                 | 6  |

| 2.1  | FPGA-based hardware accelerator design compilation approaches.          | 16 |

| 2.2  | Trend of hardware resources, their raw-computation (GMACs) and          |    |

|      | memory across different families of Xilinx FPGAs                        | 21 |

| 2.3  | FPGA memory and bandwidth hierarchy of Xilinx Virtex-7 FPGA.            | 21 |

| 2.4  | Block diagram of Xilinx dedicated DSP block (DSP48E1)                   | 23 |

| 2.5  | Illustration of pipeline, task and data parallelism in dataflow graphs. | 24 |

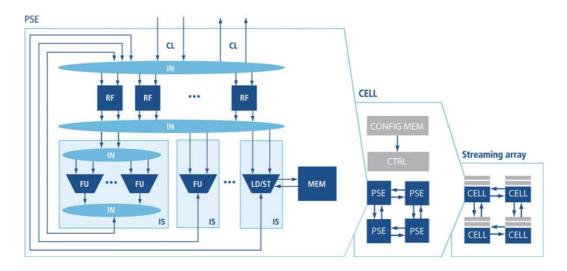

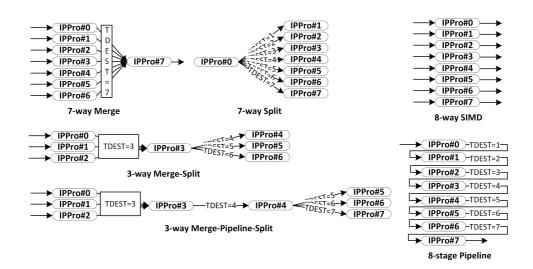

| 2.6  | Illustration of parallel computing skeletons using dataflow actors.     | 27 |

| 2.7  | The layered block diagram of Silicon Hive architecture illustrating     |    |

|      | Processing Storage Element (PSE), cell and streaming array of cores.    | 30 |

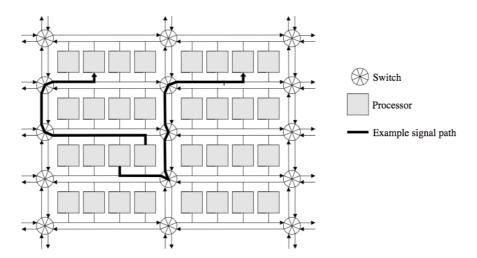

| 2.8  | The block diagram of PicoArray processors organised in a two            |    |

|      | dimensional grid connected together using a deterministic picoBus       |    |

|      | interconnect                                                            | 31 |

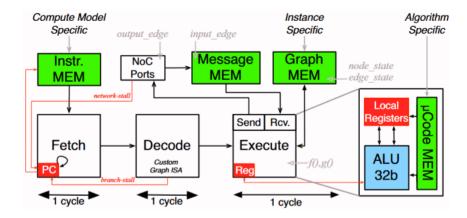

| 2.9  | Datapath of a basic pipelined processing node used in GraphSoC.         | 33 |

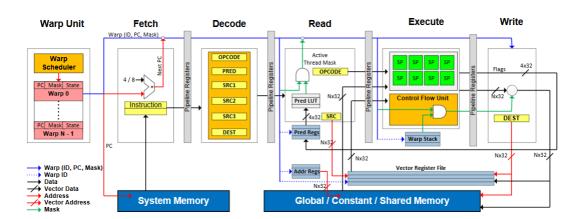

| 2.10 | Datapath of FlexGrip Streaming Multiprocessor (SM)                      | 34 |

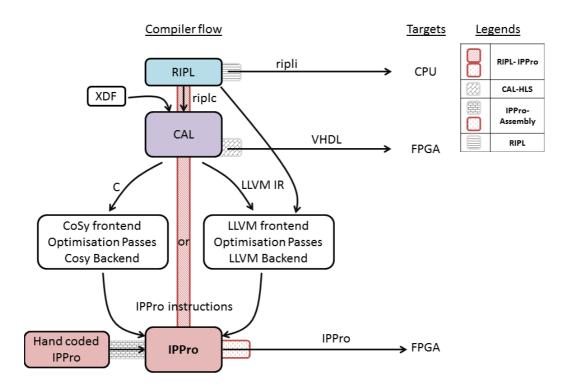

| 3.1 | Rathlin workflow of RIPL to IPPro-based platform with alterna-        |    |

|-----|-----------------------------------------------------------------------|----|

|     | tive compilation paths                                                | 41 |

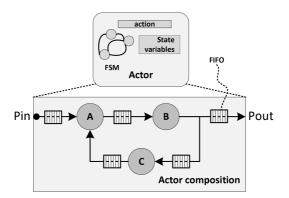

| 3.2 | Block diagram of a CAL dataflow actor and its components              | 43 |

| 3.3 | Producer-consumer driven data exchange patterns                       | 45 |

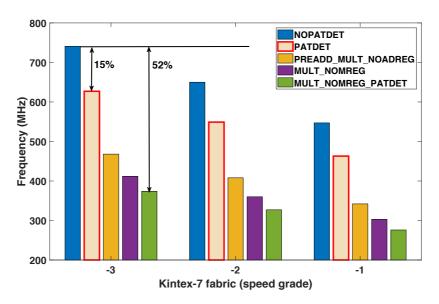

| 4.1 | Impact of DSP48E1 configurations on maximum achievable clock          |    |

|     | frequency $(f_{Max})$ using different speed grades of Kintex-7 FPGAs. |    |

|     | The DSP48E1 configuration used are: fully pipelined datapath          |    |

|     | with no pattern detector (NOPAT), with pattern detector (PAT-         |    |

|     | DET), multiply with no output register MREG (MULT_NOMREG)             |    |

|     | and pattern detector (MULT_NOMREG_PATDET) and a Multi-                |    |

|     | ply, pre-adder, no ADREG (PREADD_MULT_NOADREG)                        | 54 |

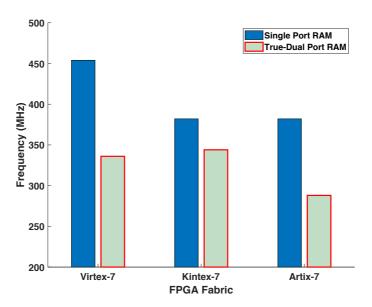

| 4.2 | Impact of BRAM configurations on the maximum achievable clock         |    |

|     | frequency $(f_{Max})$ of Artix-7, Kintex-7 and Virtex-7 FPGAs for     |    |

|     | single and true-dual port RAM configurations                          | 55 |

| 4.3 | Dataflow models (a) DFG node without internal storage ① (b)           |    |

|     | DFG actor without internal storage $t1$ and constant $i$ ② (c) Pro-   |    |

|     | grammable DFG actor with internal storage $t1, t2$ and $t3$ and con-  |    |

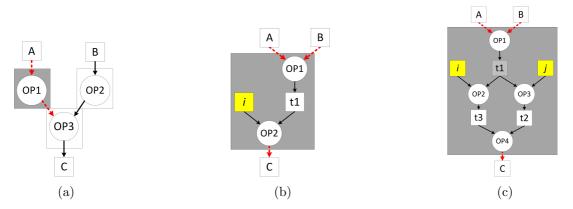

|     | stants $i$ and $j$ ③                                                  | 57 |

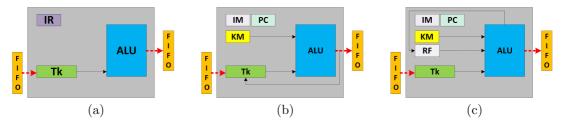

| 4.4 | FPGA datapath models (a) Programmable ALU (1) (b) Fine-grained        |    |

|     | processor ② (c) Coarse-grained processor ③                            | 57 |

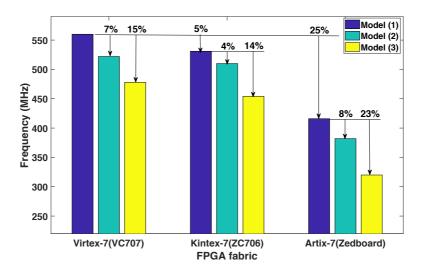

| 4.5 | Impact of datapath models ①, ②, ③ on $f_{Max}$ across FPGA fabrics.   | 60 |

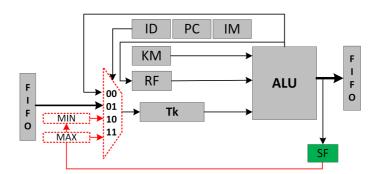

| 4.6 | Block diagram of FPGA-based soft-core processor IPPro datapath.       | 62 |

| 4.7 | Implementation of dataforwarding exploiting MACC functionality        |    |

|     | of DSP48E1                                                            | 66 |

#### LIST OF FIGURES

| 4.8  | Optimisation of IPPro datapath to support dedicated minimum                                                       |

|------|-------------------------------------------------------------------------------------------------------------------|

|      | and maximum instructions                                                                                          |

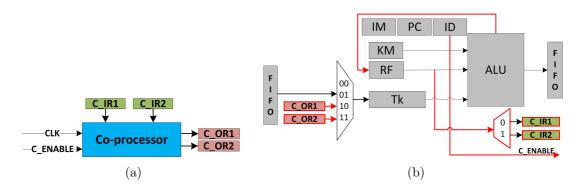

| 4.9  | (a) Input/output interfaces of division coprocessor (b) Coprocessor                                               |

|      | extended IPPro datapath                                                                                           |

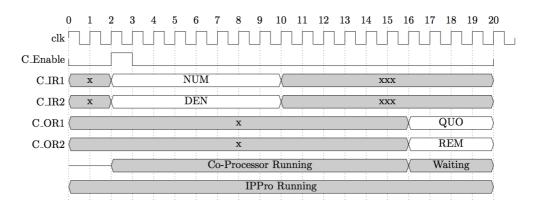

| 4.10 | Pipelined execution of division coprocessor                                                                       |

| 4.11 | Block diagram of programmable video processing platform to im-                                                    |

|      | plement case-studies using single-core IPPro                                                                      |

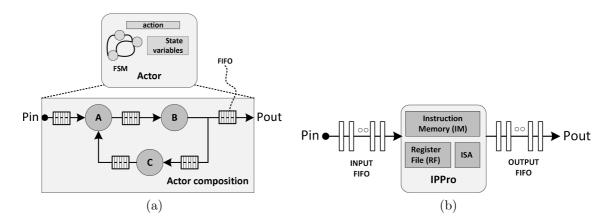

| 5.1  | (a) Representation of a CAL dataflow actor (b) Mapping of dataflow                                                |

|      | actor onto IPPro datapath                                                                                         |

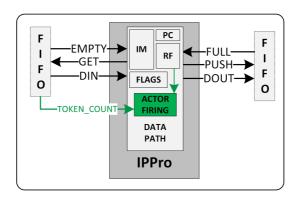

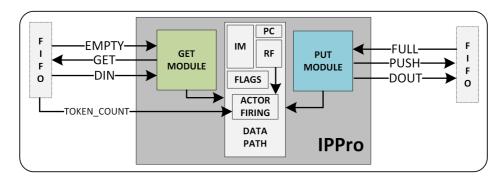

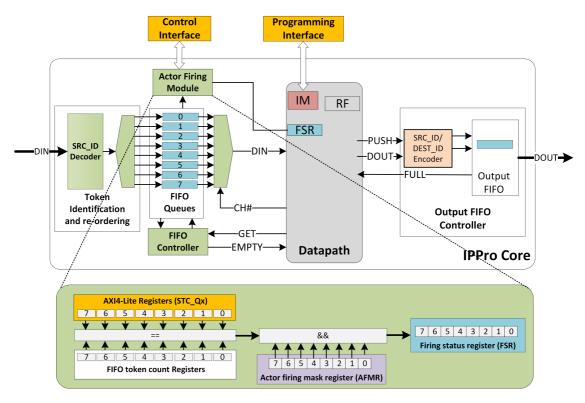

| 5.2  | IPPro datapath supporting firing of dataflow actor                                                                |

| 5.3  | Producer-consumer data-driven execution using IPPro core 94                                                       |

| 5.4  | Impact on $f_{Max}$ of realising FIFOs using different resources and                                              |

|      | configurations                                                                                                    |

| 5.5  | Mapping of dataflow execution patterns on IPPro core 98                                                           |

| 5.6  | Pseudo IPPro code to implement dataflow execution patterns 98                                                     |

| 5.7  | Block diagram of multi-port input data interface of IPPro datapath. 99                                            |

| 5.8  | Impact of multi-port IPPro datapath on execution time (in clock                                                   |

|      | cycles) of dataflow actor                                                                                         |

| 5.9  | Multiple IPPro core-based hardware accelerator designs (a) De-                                                    |

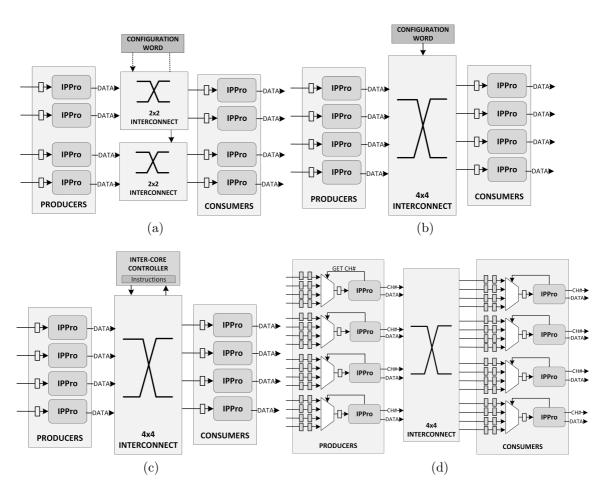

|      | sign $\textcircled{A}$ (b) Design $\textcircled{B}$ (c) Design $\textcircled{C}$ (d) Design $\textcircled{D}$ 105 |

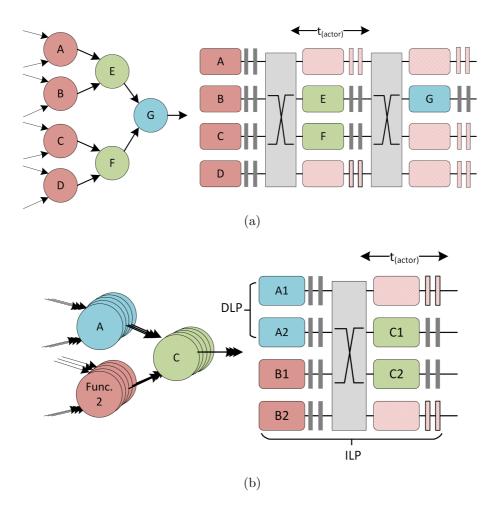

| 5.10 | Multiple IPPro cores as dataflow accelerators deploying dataflow                                                  |

|      | optimisations (a) One-to-one actor-core mapping (b) 2-way SIMD                                                    |

|      | mapping per actor                                                                                                 |

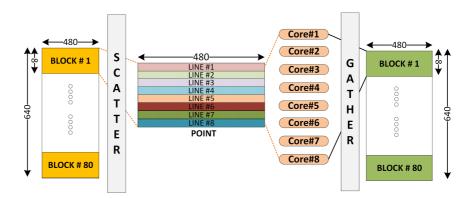

| 5 11 | Cyclic row-wise image/video pivel distribution 112                                                                |

#### LIST OF FIGURES

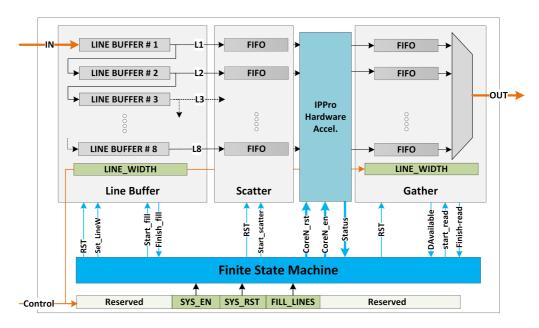

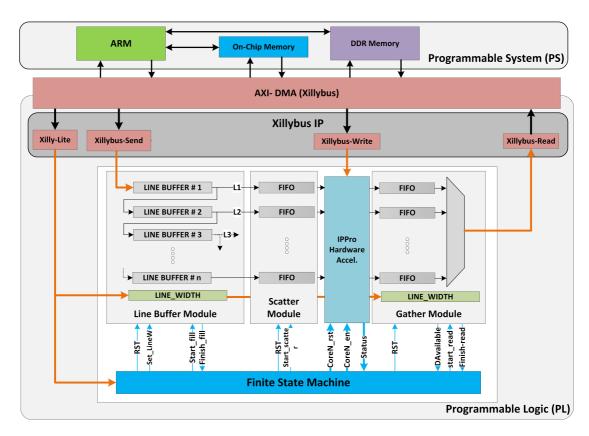

| 5.12 | System level data distribution and control architecture $113$            |

|------|--------------------------------------------------------------------------|

| 5.13 | FSM used to control the architecture of Fig. 5.14                        |

| 5.14 | Block diagram of implemented system architecture for case study. 116     |

| 5.15 | IPPro hardware accelerator designs to explore and analyse the im-        |

|      | pact of parallelism on area and performance. ① Single core IPPro,        |

|      | ② 8-way SIMD IPPro, ③ Dual core IPPro, ④ Dual core 8-way                 |

|      | SIMD IPPro                                                               |

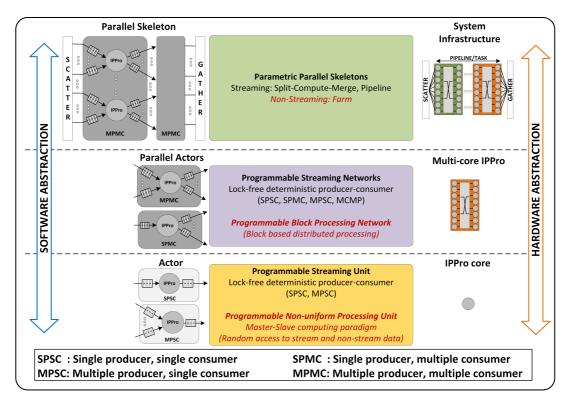

| 6.1  | Software and hardware abstraction of the platform                        |

| 6.2  | Block diagram of hardware dataflow actor firing module 135               |

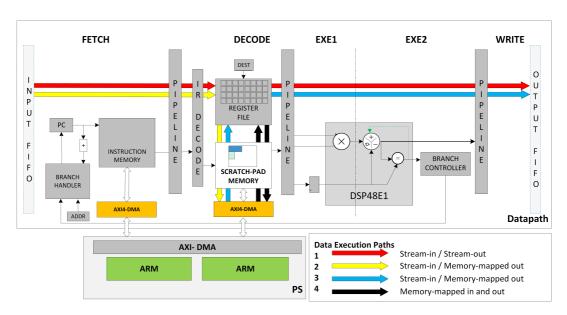

| 6.3  | Data processing paths of the IPPro using scratchpad 137                  |

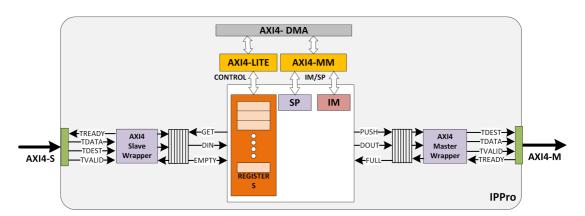

| 6.4  | AMBA-AXI4 compliant management interfaces of the IPPro 139               |

| 6.5  | Theoretical mapping of data exchange patterns on IPPro cores 143         |

| 6.6  | Realisation of data exchange patterns using stream interconnect 144      |

| 6.7  | Stream interconnect architectures with increasing core connectivity. 146 |

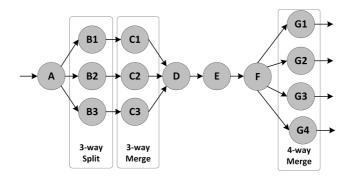

| 6.8  | A dataflow graph example that covers pipelining of multiple data         |

|      | parallel actors                                                          |

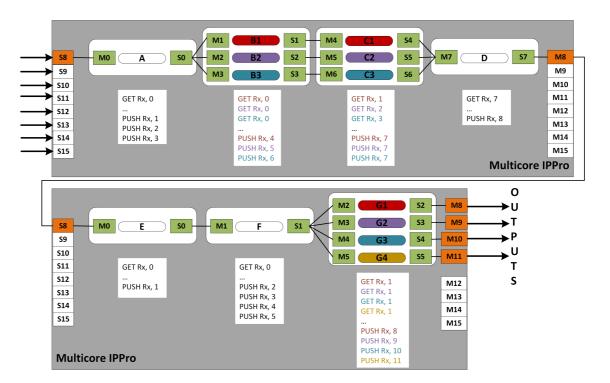

| 6.9  | Flat illustration of mapping and execution of pipelined multiple         |

|      | data parallel actors exploiting parallelism using multicore IPPro.       |

|      | The listed IPPro code shows the read, write and tagging of tokens        |

|      | for each actor. These tags are used by the interconnect to route         |

|      | token among cores of the multicore IPPro                                 |

| 6.10 | Parallel distribution of row-wise cyclic image pixels                    |

| 6.11 | Generation and distribution of the point or window pixels 155            |

#### LIST OF FIGURES

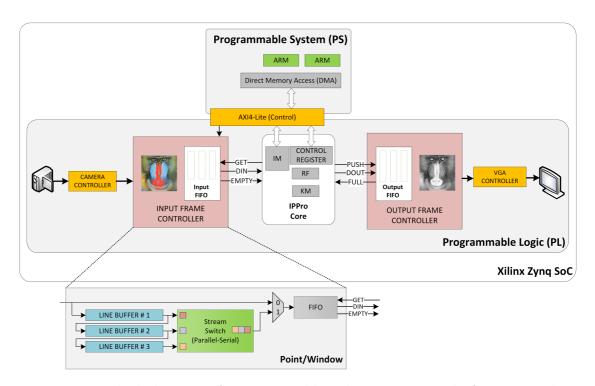

| 6.12 | Block diagram of programmable hardware acceleration platform.                                      |

|------|----------------------------------------------------------------------------------------------------|

|      | The diagram only shows a single multicore IPPro due to space                                       |

|      | limitations. Cascading of multiple multicore IPPro cores is possible                               |

|      | permitted to FPGA area resources                                                                   |

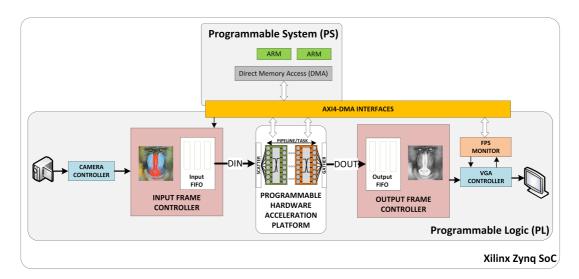

| 6.13 | $\label{thm:continuous} \mbox{Video processing system architecture using FPGA-based programmable}$ |

|      | hardware acceleration platform                                                                     |

# Chapter 1

## Introduction

Image Processing has been a field of academic research over the past several decades and is extensively employed to interpret meaning from images or video. A vast majority of electronic systems from automotive industry to factory automation, medical and surveillance employs image processing to provide intelligent analysis of their systems and improve productivity. The processing demands of such workloads often surpass the capacity of traditional computing architectures.

Video analytics is the branch of embedded vision that analyses human activity and extracts information from video content that is meaningful as perceived by the human eye. It is gaining traction in a diverse set of application markets including retail, transportation, consumer, smart-cities, critical infrastructure, and enterprise, among others. These systems use smart cameras with on-board image pre-processing to process data and give a reduction in data bandwidth and memory requirements before sending it to the centralised, server-based software platforms [1], [2]. These platforms are being aided by advanced algorithms to interpret and analyse meaning of an ever-growing increase of video content.

There is a significant amount of investment in industrial and educational research, which is expected to grow in coming years considerably. The *Embedded Vision Alliance* has estimated that the revenue from analytic video hardware, software and services will increase from \$858 million to nearly \$3 billion by 2022, representing a compound annual growth rate (CAGR) of 19.6% [3]. This growth brings significant challenges to explore new parallel computing architectures in general and image processing architecture in particular, which are portable, efficient and easier to use for a wide range of application developers.

#### 1.1 Research problem

The increasing demands for computation and bandwidth of existing and next-generation image processing applications pose severe challenges to both hardware and software solutions. While special purpose, hardware such as the *Graphics processing unit* (GPU) can handle the increasing computational demands of these data intensive applications, they come at the expense of higher power consumption, longer design times and significant programming effort. However, rapid advances and changes in state-of-art technology for these applications quickly make obsolete a dedicated accelerator or chip. The obsolescence is especially true in case of *Application-specific integrated circuit* (ASIC).

Field-programmable gate array (FPGA) technology has evolved significantly over the years from simple regular arrangements of configurable logic blocks and routing to a heterogeneous system-on-chip (SoC). Much of this improvement has inevitably been driven by market segments where FPGAs are particularly prevalent in signal processing due to pipelining and parallelism that they offer. While

the technology gap between ASIC and FPGA is widening, most of new ASIC designs lag behind due to overall design effort, time and cost making FPGA more attractive. FPGAs are proven computing platforms that offer reconfigurability, concurrency and pipelining. GPUs seem a viable highly programmable platform but, current energy requirements and limitations of *Dennard scaling* have acted to limit clock scaling, thus limits processing capabilities [4].

Apart from FPGA being a high performance and power efficient computing technology, they have not been accepted as a mainstream computing platform. The primary inhibitor is the need to use specialist programming tools, describing algorithms in hardware description language (HDL) and lack of adaptability. Silicon vendors started to alleviate this issue by introducing high-level programming tools such as Xilinx's Vivado High-level Synthesis (HLS) and Intel's (Altera's) compiler for OpenCL. While the level of abstraction has been raised, a gap still exists between adaptability, performance and efficient utilisation of FPGA resources. Nevertheless, the FPGA design flow still requires design synthesis and place-and-route that can be time-consuming depending on the complexity and size of the design; this is alien to software and algorithm developers. The development of algorithms is usually an experimental process and may require many design iterations involving quick profiling, design exploration and prototyping. In such circumstances, an FPGA design flow that requires synthesis, place-androute process is not comparable to a more familiar software-centric design flow that uses edit-compile-run. Therefore, an iterative development of a different application on FPGAs is a complicated and time-consuming process which inhibits widespread use of the technology.

The changing technology landscape and fast evolution of new application use-

cases make it imperative that underlying hardware architecture should be *adaptable*. Such platforms are a significant part of some major research initiatives where both quick prototyping and reduced design time are of prime importance. Moreover, the computing platform should allow design exploration possibilities including decomposition and mapping to optimise applications.

#### 1.2 Rathlin Project

Rathlin research project had undertaken to approach these research problems [5]. The scope of this project was to investigate the rapid developments in image acquisition/interpretation and intelligent algorithms. As they have not been matched by sound software engineering principles, to generate efficient solutions for time, memory and power efficient hardware.

A domain-specific image processing language Rathlin Image Processing Language (RIPL) for FPGAs was introduced [6]. RIPL supports algorithmic skeletons to express image processing components, which functionally inherit a dataflow model of computation. A RIPL description is converted into an intermediate dataflow language (CAL) which is mapped on to the FPGA as a network of stream processing units [7]. Though, one of the project objectives was to facilitate iterative development of different applications by replacing FPGA design flow to software-centric flow. Therefore, an adaptable FPGA-based hardware acceleration platform architecture was developed that efficiently maps and executes parallel CAL dataflow descriptions. This platform aimed to unleash the potential of state-of-art FPGAs in close synergy with a suitable software representation. Further discussion on Rathlin programming workflow and relevant background

work will be discussed in Chapter 3.

#### 1.3 Proposed approach

FPGA heterogeneous system-on-chip (SoC) architectures have addressed some of the hardware and software programming challenges [8], [9], [10]. However, fitting different parallel computational tasks onto the underlying FPGA hardware resources by using more processing nodes integrated into a single-chip is important. Besides, the need for architecture specific skills to port and optimise the applications to the underlying FPGA hardware resources which includes managing and exploiting parallelism and system heterogeneity, is also challenging. This problem is directly related to the optimal exploration of type and degree of parallelism among multiple processing nodes available within a heterogeneous system. Realising parallel applications on these heterogeneous platforms often involves design and development of the processing nodes or hardware accelerators. They can comprise fixed, reconfigurable or software programmable processors or combinations thereof. The adaptability of the underlying platform depends on the flexibility and programmability of its processing nodes. This adaptability can be present in the device, in the circuit, in the micro-architecture, in the system or even in the runtime software layer or among all of these.

This research work proposes an FPGA-based programmable hardware acceleration platform. It is a system architecture that takes advantage of heterogeneous computing. The FPGA glue logic can be used as a programmable hardware acceleration architecture that substitutes the traditional FPGA design flow (synthesis and place-and-route) to a software-centric edit-compile-run design flow [11].

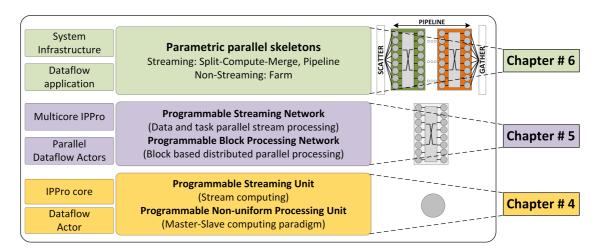

FPGA-based soft-core processor architectures have been used [12], [13], [14], [15], [16] as they offer better software controlled functionalities, system flexibility/portability, and partitioning of hardware-software co-design over other approaches [17]. The programmable hardware acceleration architecture is a three-layer architecture as illustrated in Figure 1.1 and outlined below:

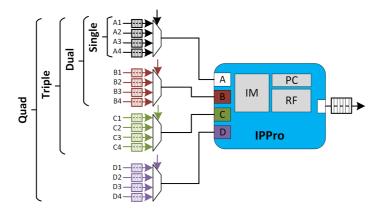

- The bottom layer is comprised of a novel FPGA-based soft-core *Image Processing Processor* (IPPro) architecture tailored to accelerate image preprocessing applications. It supports both shared memory and message passing data processing models. The IPPro core is an independent, self-managed, programmable hardware accelerator that handles the exchange of data among multiple producers and consumers by executing stream instructions. It is used as a basic computational unit of the proposed platform as shown in Figure 1.1.

- The middle layer is composed of multiple IPPro cores connected with an

Figure 1.1: Hierarchical illustration of hardware and software abstraction supported by each layer of the proposed programmable hardware acceleration architecture.

interconnect called **multicore IPPro** as shown in Figure 1.1. It extends both shared memory and stream processing and is supported by the lower layer to realise parallel computing models. The interconnect provides a deterministic, self-synchronising programmable inter-core communication mechanism to facilitate implementation of graph modelling various kinds of parallel/concurrent activities. The shared memory model offers programmable explicit synchronisation mechanism between each IPPro core and host processor to realise distributed computing and coprocessor activities.

• The top layer provides **system infrastructure** that distributes and collects data to the bottom layers. These mechanisms are necessary for efficient implementation of different parallel applications exploiting data and task parallelism as shown in Figure 1.1. Besides, it provides parametric/software configurable and dynamic data and control mechanisms to use common parallel algorithmic skeletons (split, compute and merge, farm and pipeline) and image processing operations (point and area) utilising the architectural features and processing capability provided by the bottom two layers.

The proposed approach provides a hierarchical abstraction to hardware computing resources, and the relevant communication and data access mechanisms that help to address the challenges faced by algorithm and software developers to adopt FPGAs. This approach also enables parallel exploration, profiling and implementation of different image processing algorithms to achieve the required goals.

#### 1.4 Thesis Contributions

The following are the notable contributions presented in this thesis work:

- 1. Design and development of novel FPGA-based Image Processing Processor (IPPro) soft-core architecture tailored for acceleration of image preprocessing applications. The architecture is carefully designed to support functional computing requirements of image processing while maintaining efficient utilisation of FPGA compute and memory resources. The architecture supports both message passing and shared data models enabling stream and batch processing of uniform and non-uniform distributed data. These data processing paths provide architectural features to facilitate implementation of a split, compute, merge, pipeline and farm parallel computing skeletons. Using IPPro as a fundamental computing element makes the FPGA-based platform flexible and adaptable. It allows deployment of edit-compile-run flow avoiding design synthesis and place-and-route that reduces design time.

- 2. Design and development of IPPro-based hardware accelerator models to identify the architectural requirements of the accelerator's management and provisioning policies, and their impact on the timing results of the processor. IPPro is designed as an independent, self-managed, programmable dataflow accelerator. The program code embeds both the actor's functional description and its interaction with multiple producers and consumers. It avoids the need for external control mechanisms necessary to synchronise interaction between actors while exchanging data tokens and minimises IP-Pro core management and control overheads. It gives better controllability

on the actor's token production and consumption rate and implements different data exchange patterns (split and merge). Besides, it enables fine and coarse-grained mapping and execution of data and control flow graphs which are commonly found in image processing applications.

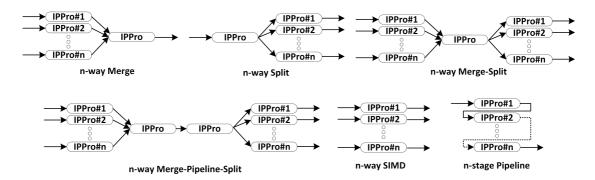

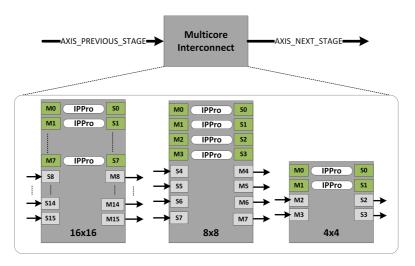

- 3. Development of a multicore IPPro architecture that provides flexible connectivity among multiple IPPro cores and enhances platform's programmable computing and mapping capabilities to map dataflow applications. The architecture complements the supported features of IPPro core and provides dynamic routing of dataflow streams among multiple IPPro cores. The connectivity among cores allows adaptable implementations of one-to-many, many-to-one, many-to-many producer-consumer dataflow graphs utilising the same hardware resources. These architectural features facilitate application profiling, optimisation options to the software and algorithm developer by exploiting data, task and pipeline parallelism.

- 4. Design and development of FPGA-based software controlled data distribution and collection architecture supporting different image resolutions. It divides an image stream into a variable number of parallel data streams that can be fed across multiple IPPro cores to realise a parallel computing paradigm. The architecture is independent, self-managed and can be integrated with both direct and buffered video processing pipelines to distribute data across multiple processing elements which are fixed in *High-level Synthesis* (HLS) system architectures. It facilitates parallel implementation of a split, compute, merge computing skeleton using multicore IPPro.

- 5. Design and development of an adaptable FPGA-based hardware accelera-

tion platform architecture. It facilitates application exploration possibilities using flexible actor-core mapping, exploiting data and task parallelism, and realisation of parallel computing skeletons on FPGA technology. The architecture provides necessary architectural functionalities to deploy edit-compile-run flow by avoiding synthesis and place-and-route times which is helpful to profile, optimise and fast prototype both parallel and non-parallel image processing algorithms on the FPGA.

#### 1.5 Thesis Outline

The remainder of the thesis is organised as follows: Chapter 2 covers the fundamental multidisciplinary concepts of FPGA-based hardware design and implementation, and parallel computing. It includes background on parallel embedded architectures focusing on FPGA-based hardware design approaches highlighting the need of adaptable and flexible hardware architectures. This is followed by the introduction to parallel computing with a primary focus on the notion of parallelism in dataflow graphs. The literature review on different FPGA-based soft-core processor architectures using different design/programming approaches will be covered at the end of the chapter.

The presented work is a part of a larger research project called *Rathlin* and covers the underlying FPGA-based hardware architecture. Chapter 3 gives an overview of the project's scope and programming work-flow. It will help the reader to understand the bigger picture of the presented research and reasons of the adopted approach, and some of the design choices made in designing IPPro, multicore IPPro and the platform architecture.

Chapter 4 presents an FPGA-based soft-core Image Processing Processor (IP-Pro) architecture tailored to accelerate image pre-processing operations. The processor datapath has been developed after a detailed insight analysis of FPGA resources, processor functionality and dataflow models. It exploits FPGAs dedicated computing and memory resources to achieve the best balance between performance and area utilisation and enables software recompilation of FPGA by avoiding synthesis and place-and-route times. The processor datapath implementation of specific image pre-processing functions. A coprocessor extension is also implemented to integrate dedicated processing units and offload complex arithmetic operations transparently. At the end of the chapter, the performance and area results achieved by single-core IPPro is compared against a fixed high-level synthesis (HLS), FPGA-based programmable processor architecture and well-established MicroBlaze soft-core processor. The IPPro core is viable to use as a basic processing element of a programmable hardware acceleration architecture.

Chapter 5 presents IPPro as a programmable dataflow accelerator architecture that can map and execute fine and coarse-grained dataflow actor using producer-consumer computing model. These execution patterns supported by the architecture provide flexible mapping options to the user and software framework to explore and deploy different dataflow graph optimisations. It also presents a detailed analysis of management and provisioning of hardware accelerator when used in heterogeneous system architecture and their impact on the system's architectural requirements and resource utilisation.

Chapter 6 presents a heterogeneous FPGA-based programmable hardware acceleration platform architecture that supports a software-controlled implementation of parallel skeletons on hardware. The platform is composed of a host processor and tightly-coupled homogeneous FPGA-based programmable hardware accelerators (IPPro cores). The platform facilitates the implementation of the split, compute and merge, pipeline and farm parallel skeletons by providing software-abstraction to make it easy to use for the software developer. The platform covers three hardware and software abstraction layers as indicated in Figure 1.1. At the end of the chapter, the acceleration results of a set of image pre-processing micro-benchmarks and functions, covering data and task parallel balanced and unbalanced dataflow actors are presented. This allows the mapping flexibility and the system's adaptability to implement different applications and computing paradigms to be evaluated.

# Chapter 2

# Background

The changing technology landscape and fast evolution of new application usecases raises the need for adaptable and efficient hardware architectures. These architectures shall handle the processing of dynamic data workloads and at the same time provide adaptability to implement different applications. This research problem initiated the need for look into different FPGA-based design approaches and programmable architectures. This chapter covers the multidisciplinary concepts related to FPGA-based hardware design approaches, dataflow model of computation and parallel computing and reviews their background and related work relevant to the thesis.

Section 2.1 covers the background on parallel embedded architectures focusing on FPGA-based hardware acceleration approaches and details pros and cons. of the existing approaches. It will discuss benefits of FPGA technology to realise efficient hardware acceleration technology to develop programmable/adaptable architectures. Section 2.2 encompasses the basic concepts of a dataflow model of computation and presents the notion of parallelism and dataflow transformations

to achieve optimised implementations. This is followed by a discussion on parallel computing skeletons that provide high-level programming constructs suitable for software and algorithm developers in Section 2.3. Section 2.4 will review the related work on FPGA soft-core and multicore processor architectures.

#### 2.1 Parallel embedded architectures

During the last decade, multiprocessor architectures have emerged as an important computing paradigm for parallel computing [18], [19], [20], [21]. They have driven the development of advanced parallel embedded architectures [22], [23]. The trend of integrating homogeneous and heterogeneous processing units have opened various hardware-based parallel application decomposition, mapping and design exploration possibilities [24], [25], [26], [27]. Hardware architectures composed of tens and hundreds of light-weight compute units have become a commonplace not only to optimise performance [12], [13], [14], [15], [16]. At the same time, these hardware architectures present several challenges such as architecture specific skills to port and optimise the applications to the underlying architecture which includes managing and exploiting parallelism and system heterogeneity. This section covers the background study necessary to understand these challenges and FPGA-based hardware design approaches taken by the research community.

## 2.1.1 FPGA multiprocessor system-on-chip

Emerging heterogenous multiprocessor system-on-chip (MPSoC) architectures such as Xilinx Zynq-7000 and Altera Arria-V SoC integrates both software pro-

grammability of a general purpose processor (ARM) with the hardware programmability of an FPGA. The integration of the hardware and software made MPSoC architectures suitable computing platform to implement mixed functionality on a single device, and to develop adaptable embedded architectures [15], [28], [29].

Nevertheless, these heterogeneous MPSoC platforms have addressed some of the hardware and software programming challenges. However, fitting of parallel computational tasks to the underlying hardware resources by using more processing nodes integrated into a single chip is still a challenge. This problem is directly related to the optimal exploration of type and degree of parallelism among multiple processing nodes available within the heterogeneous system [12], [13], [14], [30]. Besides, optimised realisation of parallel applications using these heterogeneous platforms, it often involves design and development of hardware accelerators to meet application requirements. The architecture of these hardware accelerators can have a dynamic range of flexibility from fixed, reconfigurable, software programmable or combination of thereof. They reside on the FPGA fabric and are usually managed by a general purpose processor such as ARM Cortex-A processors [28], [29]. There are different FPGA hardware design approaches to realise such hardware accelerators, Section 2.1.2 will discuss in further details.

# 2.1.2 FPGA hardware accelerator design approaches

The silicon vendors and the research community have developed and proposed different architectures, design tools and software frameworks that ease the development of hardware accelerators. The silicon vendors tools provide a cohesive

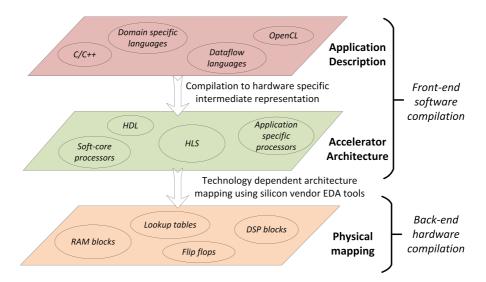

Figure 2.1: FPGA-based hardware accelerator design compilation approaches [35].

heterogeneous hardware-software co-design solution to develop and integrate the custom FPGA-based hardware accelerators. However to realise different application use case, requires architectural changes, design synthesis and place-androute [20], [21], [31], [32], [33], [34]. These design tools cover both hardware and software design space which can be divided into the front-end software compilation and back-end hardware compilation tasks as illustrated in Figure 2.1 [35]. The front-end software compilation includes application description and accelerator architecture layers. The application description can be a domain or target specific, while the accelerator architecture can encompass a wide range of hardware accelerator architectures. On the other hand, the physical mapping layer uses silicon vendor tools to physically map the chosen hardware accelerator architecture onto the FPGA resources to achieve back-end hardware compilation.

To provide programming abstraction, the application can be described in a high-level language such as C/C++, OpenCL etc. or domain-specific language

[15], [20], [36]. This application description is translated, optimised and compiled into an intermediate representation that can be mapped onto the target-hardware-A wide range of target-hardware-accelerator approaches can be adopted ranging from a highly optimised application-specific processor, a flexible and programmable soft-core processor, an overlay architecture or a combination of thereof as illustrated in Figure 2.1. Each of these approaches has their pros and cons regarding design flexibility, area and performance [12], [20], [21], [23]. Based on the chosen target-hardware-accelerator architecture, the intermediate representation can be converted either into a set of dedicated domain-specific instructions, a program code consisting of mix of a general purpose instructions, or a hardware description language (HDL) or combination of thereof. The physical layer takes the HDL description of the target-hardware-accelerator design and converts into an FPGA mappable form, i.e. to the physical resources of an FPGA (flip-flops, lookup tables, dedicated DSP and memory blocks). This task requires technology dependent optimisation and routing mechanisms which are conducted by automated silicon vendor tools. The tasks involve design synthesis, place-androute and bit-stream generation. These steps can be significantly time-consuming for iterative algorithm development depending on the complexity and size of the hardware design [8], [9], [10], [37].

#### High-level synthesis (HLS)

High-level synthesis (HLS) tools take an application description, use different analysis techniques to profile and explore the design space. The majority of these tools use a dataflow model of computation, therefore Table 2.1 lists both academic and commercial HLS tools that are widely reported in the open lit-

erature [38], [39]. These tools support different high-level languages such as C, C++, OpenCL or domain specific languages to describe an application. These tools profile, explore, optimise and compile the high-level description into an intermediate representation which is translated into hardware description languages [7], [40], [41] such as VHDL, Verilog or SystemC as listed in Table 2.1.

These tools take advantage of FPGA deep pipelining to exploit parallelism and explore performance and resource optimisations by tuning the size of the first-in-first-out FIFOs [41], [42]. The oversized buffer uses more resources than needed, while small buffer can cause additional delays, stalls, and deadlocks during execution of the application [40], [43]. Though, all HLS tools generate a fixed hardware architecture tailored to accelerate a specific application or part of an algorithm which is not adaptable. To implement different applications, the only possibility is to rewrite and go through all front-end and back-end tasks discussed in Figure 2.1. The back-end tasks can significantly increase the design time [8], [9], [21], [23], [37] which is not appealing by software and algorithm developers due to the iterative algorithm development process which requires design exploration and fast prototyping. Section 2.1.3 discusses this problem in detail.

Table 2.1: High-level Synthesis (HLS) tools for FPGAs. [38], [39].

| HLS Tool        | License    | Input            | Output               | Data | Control |

|-----------------|------------|------------------|----------------------|------|---------|

|                 |            |                  |                      | flow | Flow    |

| Catapult-C      | Commercial | C/C++/SystemC    | VHDL/Verilog/SystemC | 1    | 1       |

| Bluespec        | Commercial | BSV              | SystemVerilog        | 1    | 1       |

| C-to-Silicon    | Commercial | SystemC/C++      | Verilog/SystemC      | 1    | 1       |

| MaxCompiler     | Commercial | MaxJ             | RTL                  | 1    | X       |

| ROCCC           | Commercial | C subset         | VHDL                 | 1    | 1       |

| GAUT            | Academic   | C/C++            | VHDL                 | 1    | 1       |

| Synphony C      | Commercial | BDL              | VHDL/Verilog         | 1    | 1       |

| $_{ m LegUp}$   | Academic   | C                | Verilog              | 1    | 1       |

| Vivado HLS      | Commercial | C/C++/SystemC    | VHDL/Verilog/SystemC | 1    | 1       |

| Altera SDK      | Commercial | C/OpenCL         | VHDL/Verilog         | 1    | 1       |

| HIPAcc          | Academic   | C++ Embedded DSL | C++                  | 1    | X       |

| Merlin Compiler | Commercial | C/C++            | C/OpenCL             | ✓    | 1       |

#### 2.1.3 Need for adaptable hardware architectures

The emerging versatile application markets raise the demand for high-performance and efficient FPGA architectures, that can handle the processing of dynamic data workloads and at the same time adaptable to accelerate different applications. One way to approach this research problem is by developing adaptable FPGA hardware architecture that enables edit-compile-run flow familiar to software and algorithm developers instead of hardware synthesis and place-and-route. It can be achieved by populating FPGA logic with a light-weight and high-performance soft-core processors used for programmable hardware acceleration. This underlying architecture will be adaptable and can be programmed using conventional software development approaches as illustrated in Figure 2.1. This approach does not require hardware design synthesis and place-and-route. Instead, it will need software re-compilation that shall generate a binary code to run on the underlying soft-core processors.

Though the HLS-based designs are use case optimised as the application is known before realising the underlying hardware. On the contrary, in processor-based approach, the underlying hardware architecture is designed, synthesised, place-and-route in advance. Therefore, the overall area is expected to be more significant and performance is supposed to be lower than HLS, which will come at the cost of adaptability and reduction in design time.

This approach provides hardware abstraction of the underlying FPGA programmable resources by allowing them to reconfigure using traditional software approaches and exposes it to the software developer. It inherits software benefits such as portability, partitioning complex hardware-software co-design, decompo-

sition and mapping options to achieve desired area and performance goals. Besides, avoiding required iterative process of synthesis and place-and-route would reduce design time, improve productivity and allow software-controlled design exploration opportunities. Jain, Rigamonti and Liu have reported an order of magnitude improvements by compiling applications onto processor architectures over HDL and partial reconfiguration approaches [23], [44], [45]. Nevertheless one of the significant challenges is to efficiently compile, map and execute parallel applications onto the underlying programmable hardware accelerator architecture.

#### 2.1.4 FPGA memory and computation resources

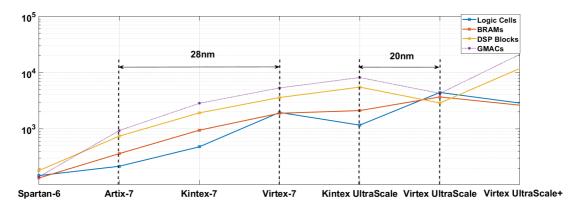

FPGA fabric provides essential digital components necessary to build any digital circuit. It has logic blocks, dedicated memory and DSP Blocks, clock management circuitry and routing resources to connect these digital components. In an FPGA, the location of these components are fixed and cannot be changed which makes it essential to consider their layout to obtain area-efficient and high-performance hardware architecture. Figure 2.2 shows the available hardware resources, their raw-computation (GMACs) and the memory resources across different families of Xilinx FPGAs. The raw-computation (GMACs) is directly proportional to the number of DSP blocks. Dinechen et al. show how to map different arithmetic operators on FPGA fabric utilising different approaches including LUT, DSP block etc. [46]. Similarly others presented mapping of mathematical expressions to these DSP blocks and achieved performance improvements [47], [48], [49].

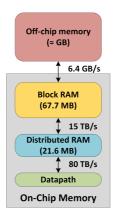

While the computing resources and bandwidth are high, the memory in FPGA is limited compared to other computing technologies. Figure 2.3 shows the distri-

Figure 2.2: Trend of hardware resources, their raw-computation (GMACs) and memory across different families of Xilinx FPGAs [50], [51].

bution of on-chip memory and bandwidth on the Virtex-7 FPGA. Moving away from the datapath the memory size increases while the bandwidth get limited. On-chip memory consists of LUT-based Distributed RAM that are small and close to the datapath which can provide faster access to data at higher bandwidth. On the other hand, Block RAM is comparatively larger but limited in bandwidth. It shows that there is a trade-off between the memory-size and bandwidth.

Focusing on the FPGA technology, the 7 series Xilinx FPGAs comes in three different families. The 7 series combine the power reducing process, design technology.

Figure 2.3: FPGA memory and bandwidth hierarchy of Xilinx Virtex-7 FPGA.

niques, and architectural enhancements to deliver the lowest-in-class power consumption, compared to the previous generation of Xilinx FPGAs. It covers a low-cost Artix-7 family, a midrange Kintex-7 family, and a high-end Virtex-7 family of FPGAs. All three families uses the same 28nm silicon process technology and have the basic FPGA building blocks of logic cells, DSP blocks, BlockRAM making it simpler to migrate designs across FPGA family. The Kintex-7 device family features a perfect balance of FPGA fabric clock rate performance versus power consumption, high-speed I/O, capacity and reliability. Artix-7 uses the same FPGA resources as Kintex-7, but optimized for even lower power consumption and smaller size packages, delivering similar advantages, at the cost of lower chip price and performance.

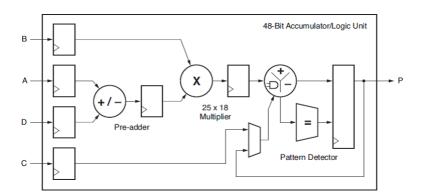

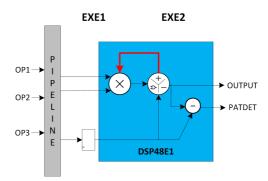

#### 2.1.5 DSP block

Most of the digital signal processing applications extensively use multiply and accumulate operations that can be performed efficiently using these DSP blocks. These blocks are uniformly-distributed inside the FPGA fabric. They are capable of performing basic arithmetic and logic operations on data that is suitable to design efficient, high-performance arithmetic logic unit (ALU) of a processor. Xilinx DSP Block (DSP48E1 and DSP48E2) supports these operations and can be dynamically configurable in contrast to Altera. Figure 2.4 shows the simplified functional block diagram of the DSP48E1. It has four main arithmetic blocks:

- 1. 25-bits Pre-Adder

- 2. 25x18 bits Multiplier

- 3. 48-bits Adder, Subtractor, Logical

Figure 2.4: Block diagram of Xilinx dedicated DSP block (DSP48E1) [52].

#### 4. Comparator and pattern detector

The DSP48E1 is capable of multiply, multiply- accumulate, add, subtract and other operations. Besides, a set of control registers that allow controlling the internal datapath on a cycle-to-cycle basis (for details see Appendix B Table B.1). There are pipeline registers that enable/disable the internal pipelining of the DSP48E1 block and improve the timing of the block by reducing the critical path [52]. Three internal multiplexers allow mapping of input and output operands to multiplier and adder/subtracter.

# 2.2 Dataflow model of computation

In early 1970s, various classes of model of a computation (MoC) had been introduced that models the architecture independent functional requirements through semantics, interfaces and provides synergy between processing units [53], choosing a suitable MoC is one of the key hardware design decision. The dataflow MoC could possibly be expressive programming and efficient execution model. It has the property to express applications as network processes which offer parallelism

scalability, modularity, portability and adaptivity. These characteristics are vital to unify the system level design of heterogeneous platforms. Moreover, it follows the principle of stream processing [22] that are suitable for FPGA-based hardware architectures [54], [55], [56], [57].

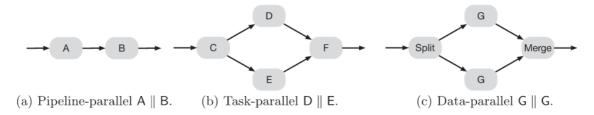

#### 2.2.1 Notion of parallelism in dataflow graphs

Stream and dataflow driven programming models allows efficient implementation of different types of parallelism [30], [58], [59]:

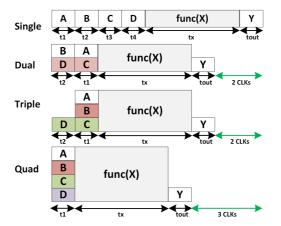

**Pipeline parallelism** A pipeline is a chain of actors  $a_1, \ldots, a_n$  that are directly connected in the stream graph. Each pair  $(a_i, a_{i+1}), i \in \{1, \ldots, n-1\}$  has a producer/consumer relationship, that is,  $a_i$  consumes items produced by  $a_{i-1}$  and produces items that serve as input for  $a_{i+1}$ . Figure 2.5 shows a pipelined execution of function A and B. It is important to note that the throughput shall only be as fast as the slowest group of actors in the pipeline [60].

Task parallelism Two actors  $a_1, a_2$  are task parallel if they are on different branches of the stream graph. In contrast to pipelines, there are no input/output dependencies between  $a_1$  and  $a_2$ . Figure 2.5 shows task parallel actor D and E.

Data parallelism is the property of an actor to have no dependencies between

Figure 2.5: Illustration of pipeline, task and data parallelism in dataflow graphs [58].

one execution and the next. The actor can be replicated by using multiple instances of an actor such as G is replaced twice as shown in Figure 2.5.

#### 2.2.2 Dataflow transformation

Dataflow transformations are frequently used to enhance system performance, by improving the performance of slower dataflow nodes or part of the graph [24] [26]. These transformations maintain the functionality of original dataflow graph, but increase the throughput or decrease the latency [26], [30]. Dataflow graphs are amenable to coarse-grained transformation to exploit data, task and pipeline parallelism that can be efficiently implemented using FPGA [24]. Single instruction multiple data (SIMD) based hardware architectures had been used to accelerate applications including image pre-processing due to massive pixel processing [61], [62], [63]. The dataflow specific optimisations (decomposition, mapping, and scheduling) and transformations (fission, fusion, etc.) can be exploited to improve performance [24], [30], [64]. These transformations allow decomposition and design space exploration possibilities to achieve desired application goals. The application can map on a multicore architecture, which will enable exploiting data and task parallelism by supporting edit-compile-run design flow.

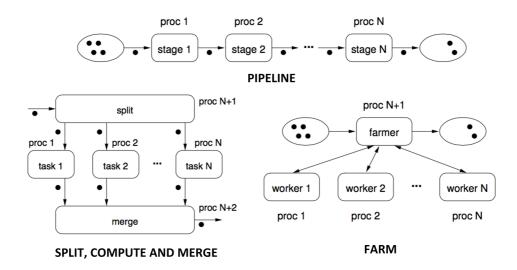

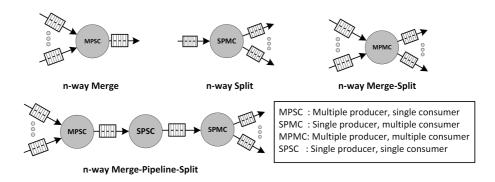

# 2.3 Parallel computing skeletons

Parallel computing skeletons capture common parallel-programming paradigms and abstract to the programmer as high-level programming constructs equipped with well-defined functional semantics [12], [65], [66], [67], [68]. They model a precise parallel pattern to exploit parallelism and hides pattern implementation

details from the programmer to exploit parallelism as shown in Figure 2.6. These patterns are *parametric* and can be *re-used* in different applications. This approach is adopted by several parallel programming frameworks [31], [69], [70].

#### 2.3.1 Pipeline

The basic idea of the *pipeline* skeleton is to split processing into a series of sequential steps, with storage at the end of each step as shown in Figure 2.6. It is possible by distributing a sequential application into multiple independent but sequential tasks, where preceding task feeds data to the following task. It enables concurrency where that tasks can execute in parallel as soon as the data is available at the processing node. The computational load of tasks may vary and is not known before run-time unless static model of computation such as static dataflow is used to define the parallel application. Though, the maximum achievable processing rate depends on the processing rate of the slowest task, which is faster than the time needed to perform all the steps at once. However, by static profiling of the application in hand, it is possible to find an efficient decomposition that could lead to balanced tasks with bounded memory requirements.

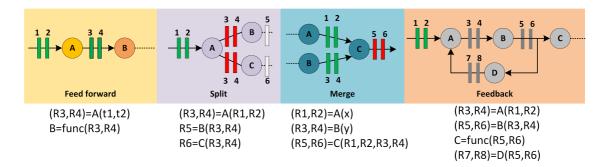

## 2.3.2 Split, compute and merge

This skeleton is used to process regularly distributed data-based on static decomposition. The data is divided into a number of equal sized blocks (row-based, column-based or block-based) where the number of parallel data blocks defines the level of exploitable data parallelism. In architectural terms, it is know as scatter-gather or split-compute and merge parallel programming model as shown

Figure 2.6: Illustration of parallel computing skeletons using dataflow actors [71].

in Figure 2.6. Moreover, it can also be extended to implement different derived multi-stage pipelined skeletons to exploit both data and task parallelism using the *pipeline*, *split*, *compute*, *communication*, *compute*, *merge* or a combination of thereof, to achieve better performance. The benefit of pipelining multiple stages is that it reduces data transfer overhead, improves data bandwidth, avoids memory bottlenecks in contrast to shared memory model-based acceleration approach where the bandwidth and cache coherency significantly degrade the performance.

#### 2.3.3 Farm

This skeleton is used to process irregular data. The farmer (host/master processor) allocates the tasks to the workers until none are left as shown in Figure 2.6. Then, the farmer waits for a result from a worker and immediately sends another work item to it. Each worker receives a work packet, process it, and returns the result to the farmer until it gets a stop condition from the farmer. The advantage of this approach is that the farmer knows which workers have yielded the results

of their tasks and are hence idle. Thus, the farmer can forward incoming tasks to the idle workers.